DC-DCコンバータにおける制御系の設計において、

- ESRの小さなセラミックコンデンサ等を用いると安定性が悪化する

- 入力電圧が大きくなるほど安定性が悪化する

などの記述を目にすることがあると思います。

初見のとき、私はパッとしませんでした。DC-DCコンバータ以外でも目にすることがあるように思います。

そこでこの記事では、降圧形コンバータの伝達関数からボード線図を描くことで考えてみます。

※ESRとは、等価直列抵抗を意味します。理想的ではないコンデンサの内部に存在してしまう、コンデンサと直列に存在すると考える抵抗分です。理想的には0Ωです。ざっくり、電解コンデンサ(円柱型のやつ)はESRが大きく、セラミックコンデンサ(チップのやつ)はESRが小さいというイメージです。

降圧形コンバータの伝達関数

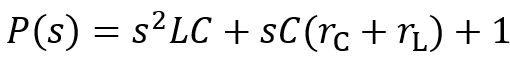

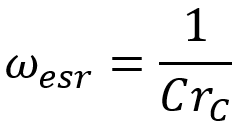

本記事では、状態平均化法を用いて導出された降圧形コンバータの伝達関数として次式を用います。

ここで、

と置かれています。

Gdvは降圧形コンバータの伝達関数、Viは入力電圧、Lはインダクタンス、Cはキャパシタンス、r_Cはコンデンサの等価直列抵抗(ESR)、r_Lはインダクタの等価直列抵抗を表します。

本記事における基準値

本記事では、以下の値を基準として用います。

例えば、ESRの変化に対するボード線図の変化を知りたいとき、ESRの値となるr_Cを変数とし、他は以下の値で固定としています。

- Vi = 3.3V

- L = 4.7μH

- r_L = 20mΩ

- C = 100μF

- r_C (ESR) = 1mΩ

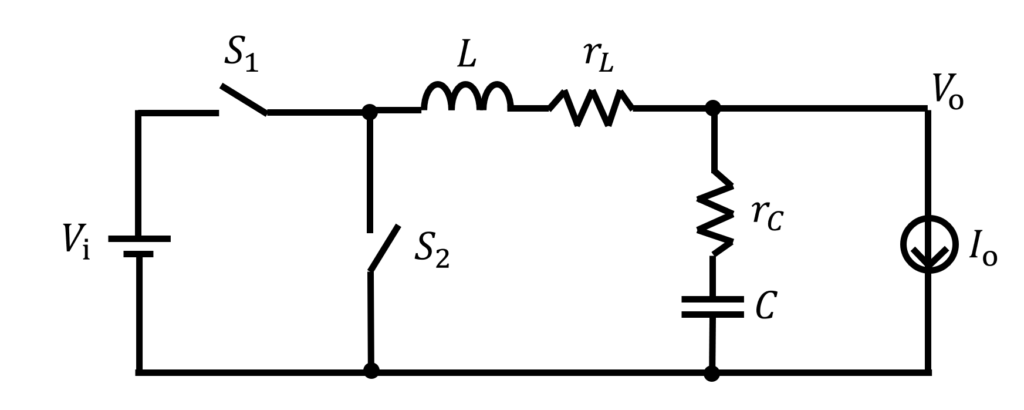

ESRの変化に対するボード線図の変化

- ESRの小さなセラミックコンデンサ等を用いると安定性が悪化する

について確認してみます。

ESR = 1mΩ、10mΩ、50mΩと変化させたときのボード線図です。

ESRが大きくなると、位相の遅れが抑えられています。(位相の戻りが良い)

安定余裕(ここでは位相余裕)は、一巡伝達関数におけるゲイン曲線が0dBとなる点(ゲイン交差周波数)で、位相が-180°からどれだけ上にあるか(位相余裕)をみます。上にあればあるだけ安定です。

今回、見ているのは降圧形コンバータの伝達関数だけであるので、実際のゲイン交差周波数とはことなります。そこで、交差周波数があるであろう高い周波数をおおまかに着目してみます。ESRが大きいほど-180°より上に向かうため、安定な制御系を作りやすそうです。

1mΩでは、高域で-180°付近に張り付いていて、補償器をしっかり設計しないと発振しそうですね。

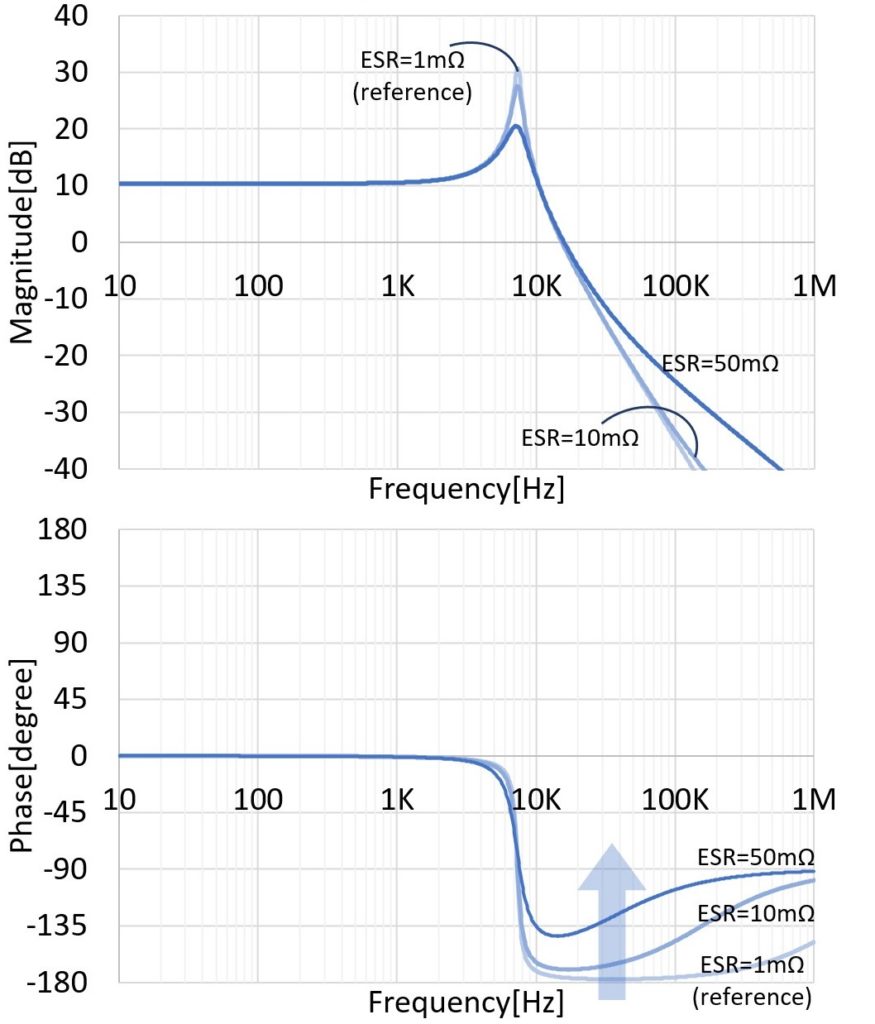

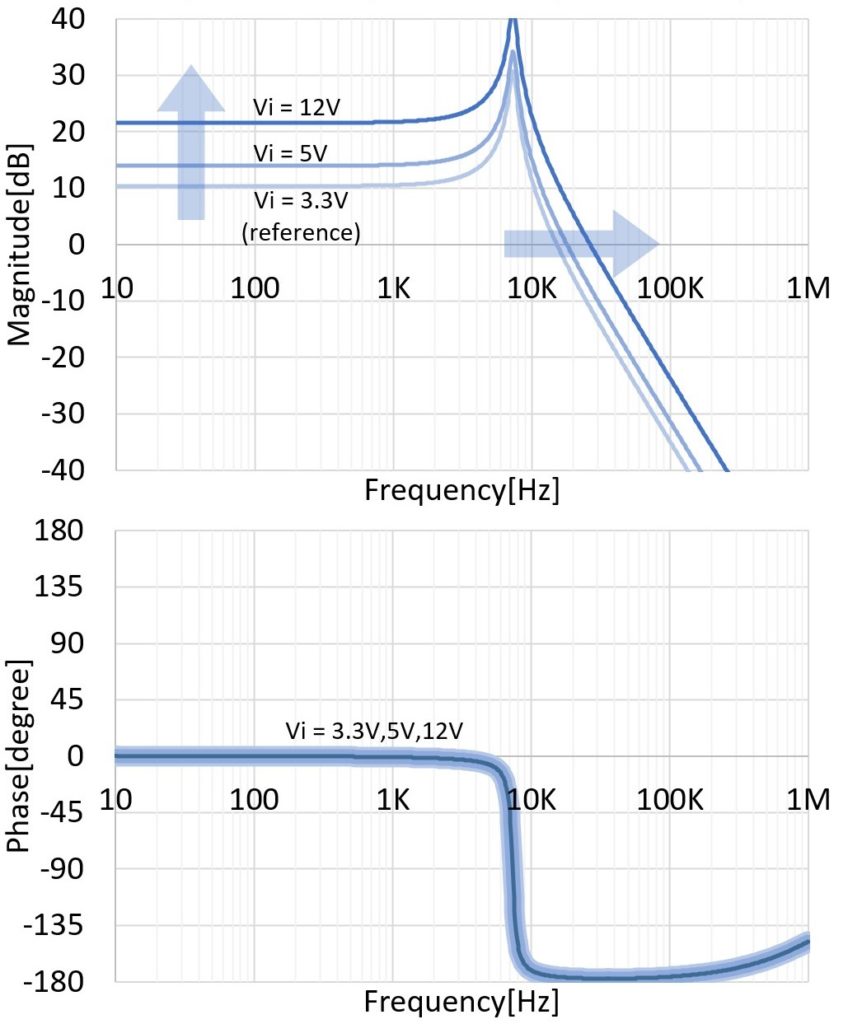

入力電圧の変化に対するボード線図の変化

- 入力電圧が大きくなるほど安定性が悪化する

について確認してみます。

入力電圧Vi = 3.3V , 5V , 12Vと変化させたときのボード線図です。

位相線図に変化はありませんが、ゲイン線図に変化が見られます。

ゲイン線図では、入力電圧が大きいほど、ゲイン曲線が正の方向へシフトしています。

これに伴い、ゲイン交差周波数が高い周波数へシフトしています。

この結果、ゲイン余裕が小さく、位相余裕が小さくなる恐れがあります。

よって、安定余裕が悪化する可能性があるというわけです。

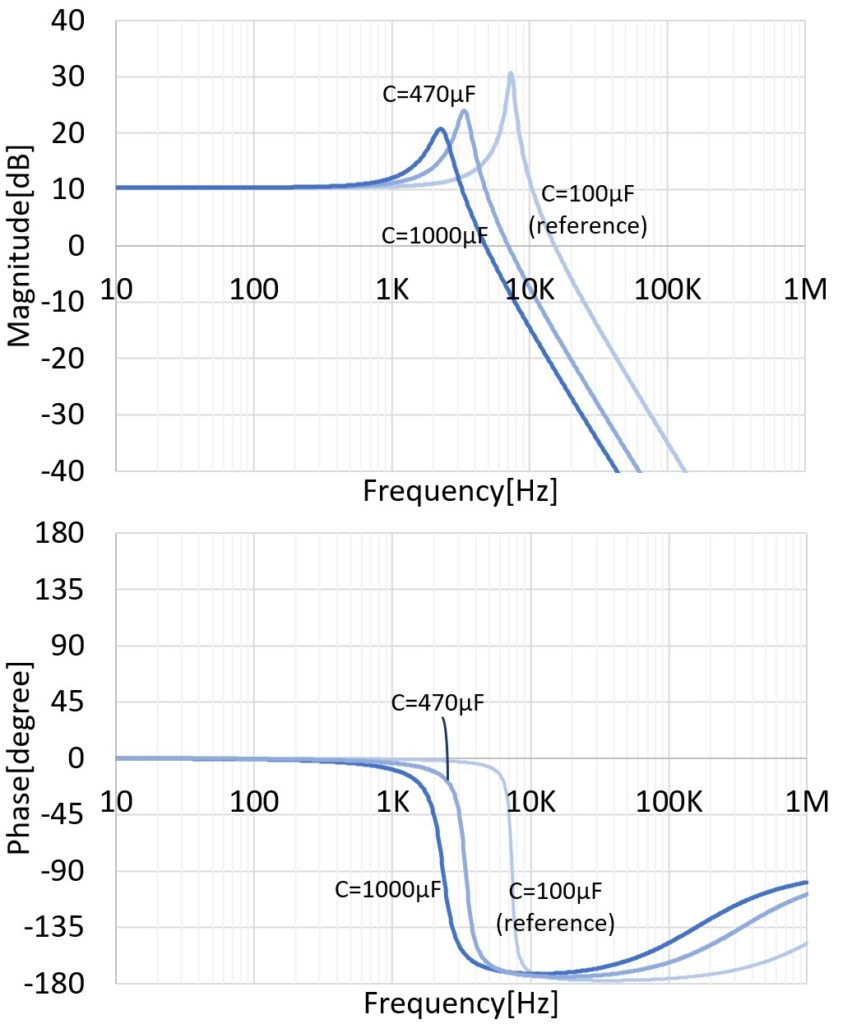

付録

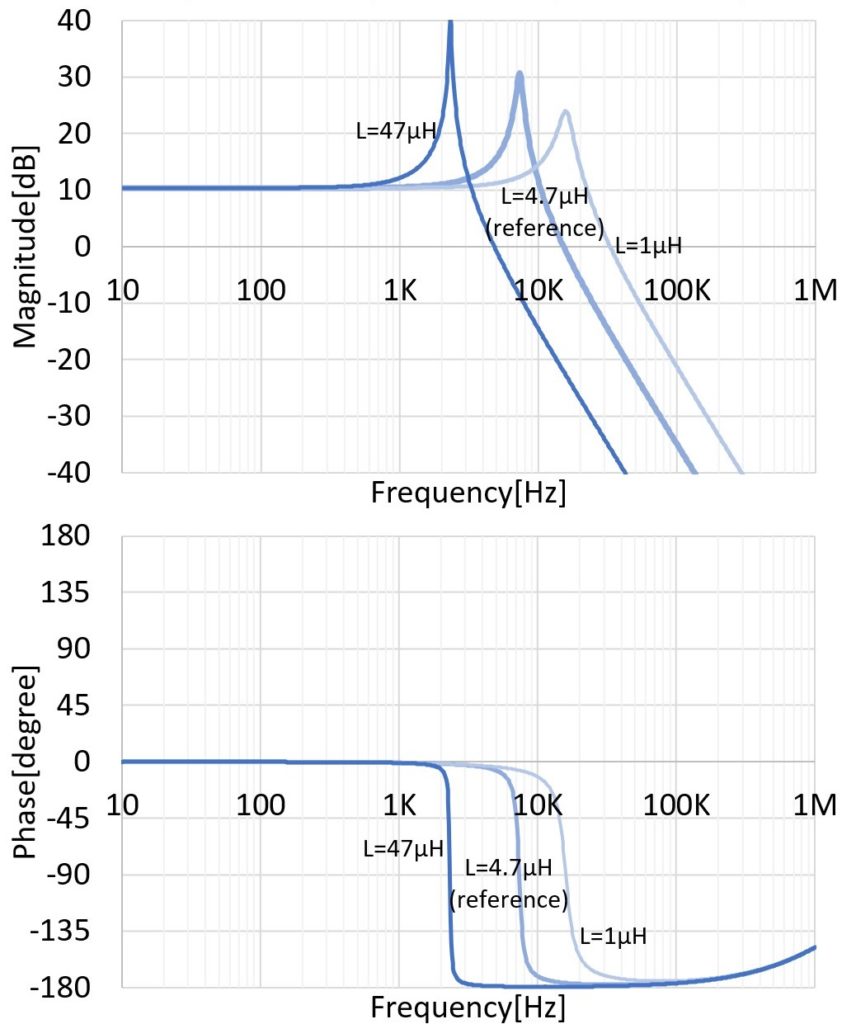

コンデンサ(キャパシタンス)の変化に対するボード線図の変化

インダクタ(インダクタンス)の変化に対するボード線図の変化